摘要:可编程片上系统(SoPC)设计是一个崭新的、富有生机的嵌入式系统设计方向。嵌入式集成化设计已成为电子领域发展的一个重要方向。Xilinx提供的EDK正是用于创建基于FPGA的嵌入式系统的开发工具包。本文介绍基于SoPC的波形发生器在EDK工具包下的设计与实现。本设计采用嵌入式软处理器核 MicroBlaze以及自主编写的包括实现DDS在内的多种IP Core,最大限度地实现系统的集成化。

关键词:SoPC IPCore EDK MicroBlaze DDS 波形发生器

引 言

SoPC可编程片上系统是一种特殊的嵌入式微处理器系统。首先,它是片上系统(SoC),即由单个芯片完成整个系统的主要逻辑功能;其次控制工程网版权所有,它是可编程系统,以FPGA为硬件基础,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件系统在线可编程的功能。

IP(Intellectual Property)

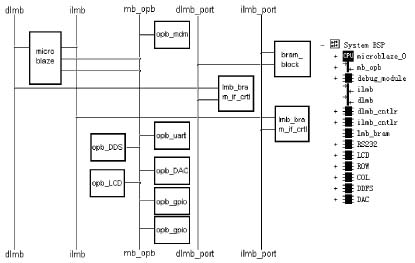

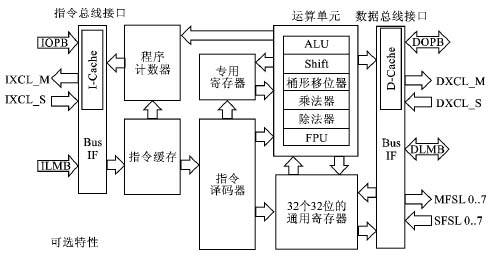

对于本设计来说,利用SoPC和IP的优势是可以利用最少的元器件,创建一个易配置、易扩展、易修改并且易于继承使用的集成系统。该系统的创建是基于Xilinx公司提供的嵌入式开发工具包EDK(Embedded Development Kit)来实现的。EDK自带了MicroBlaze软核和PowerPC硬核微处理器及大量免费IP,有利于构建简易系统。针对MicroBlaze及PowerPC提供的C语言编译器,可使系统的功能实现更加简易。对基于MicroBlaze的系统,MicroBlaze通过OPB总线与外设IP及外部存储器控制接口相连接,通过LMB(Local Memory Bus)总线与FPGA片上块存储器BRAM(Block RAM)相连接,还可以通过EMC(External Memory Control)等存储器控制IP扩展片外RAM或ROM。

1 系统的架构

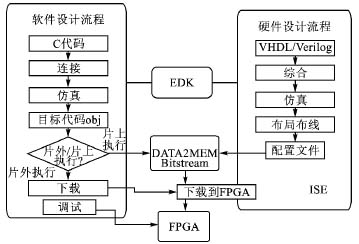

本设计采用SoPC可编程片上系统的思想,利用Xilinx的Spartan3系列XC3S400 FPGA,通过EDK开发工具包的集成开发环境XPS(Xilinx Platform Studio)完成了FPGA硬件系统设计及基于此硬件系统的软件开发。图1是基于EDK的系统开发设计流程图,设计分为硬件设计和软件设计两部分。硬件设计符合基于HDL硬件描述语言的EDA开发流程控制工程网版权所有,是根据硬件系统合理使用总线IP和外设IP,并为各个实例定义地址范围以及输出端口和时钟CONTROL ENGINEERING China版权所有,经过综合及布线后形成硬件配置文件。软件设计与传统的嵌入式软件开发设计类似,是在硬件设计的基础上根据处理器所支持的指令集以及编译环境编写程序代码,然后对代码编译烧写及调试。

图1EDK系统开发流程图

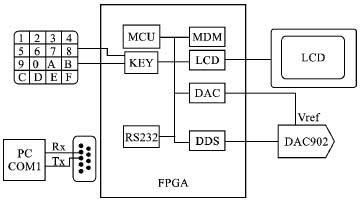

该设计通过FPGA实现所有数字部分。系统的示意图如图2所示。

图2系统示意图

图3FPGA内部的硬件系统

图4MicroBlaze处理器架构图

在FPGA内部,以MicroBlaze为控制核心,以DDS IP为波形发生功能实现核心,同时加入了其他的IP核,诸如调试用的MDM(Microprocessor Debug Module),用于与PC进行通信的UART(Universal Asynchronous Receiver & Transmitter)通用异步传输模块,以及LCD显示和4×4按键控制模块,实现了系统的高度集成。FPGA硬件系统为数字系统产生数字量CONTROL ENGINEERING China版权所有,外围电路加上高速数模转换器件DAC902,把波形数据转换为模拟波形控制工程网版权所有,即实现了完整的可编程片上系统的波形发生器。

&n

在线会议

在线会议 论坛

论坛 专题

专题 工控直播

工控直播 新闻中心

新闻中心 子站

子站 技术

技术 社区

社区

中控时间序列大模型TPT免费有奖体验

中控时间序列大模型TPT免费有奖体验 爱德克SE2L进阶版安全激光扫描仪有奖预约演示

爱德克SE2L进阶版安全激光扫描仪有奖预约演示 剑维软件电子半导体行业白皮书有奖下载

剑维软件电子半导体行业白皮书有奖下载 魏德米勒麒麟系列产品赋能本土工业

魏德米勒麒麟系列产品赋能本土工业 Fluke 283 FC 智能万用表震撼来袭

Fluke 283 FC 智能万用表震撼来袭