1 简 介

Intel XScale微体系结构提供了一种全新的、高性价比、低功耗且基于ARMv5TE体系结构的解决方案,支持16位Thumb指令和DSP扩充。基于XScale技术开发的微处理器,可用于手机、便携式终端(PDA)、网络存储设备、骨干网(BackBone)路由器等。Intel PXA250微处理器芯片就是一款集成了32位Intel XScale 处理器核、多通信信道、LCD控制器、增强型存储控制器和PCMCIA/CF控制器以及通用I/O口的高度集成的应用处理器。

Intel XScale处理器的处理速度是Intel StrongARM处理速度的两倍,其内部结构也有了相应的变化:

数据Cache的容量从8KB增加到32KB;

指令Cache的容量从16KB增加到32KB;

微小数据Cache的容量从512B增加到2KB;

为了提高指令的执行速度,超级流水线结构由5级增至7级;

新增乘/加法器MAC和特定的DSP型协处理器CP0,以提高对多媒体技术的支持;

动态电源管理,

XScale微处理器架构经过专门设计,核心采用了英特尔先进的0.18μm工艺技术制造;具备低功耗特性控制工程网版权所有,适用范围从0.1mW~1.6W。同时,它的时钟工作频率将接近1GHz。 XScale与StrongARM相比CONTROL ENGINEERING China版权所有,可大幅降低工作电压并且获得更高的性能。具体来讲,在目前的StrongARM中,在1.55V下可以获得133MHz的工作频率,在2.0V下可以获得206MHz的工作频率;而采用XScale后,在0.75V时工作频率达到150MHz,在1.0V时工作频率可以达到400MHzwww.cechina.cn,在1.65V下工作频率则可高达800MHz。超低功率与高性能的组合使Intel XScale适用于广泛的互联网接入设备,在因特网的各个环节中,从手持互联网设备到互联网基础设施产品,Intel XScale都表现出了令人满意的处理性能。

2 PXA250的结构及特点

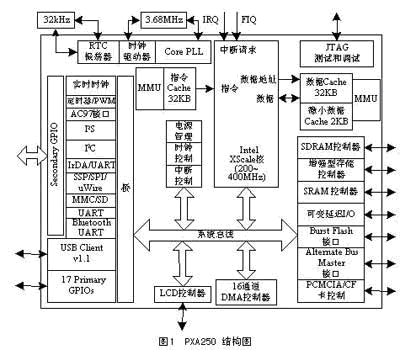

Intel XScale PXA250结构框图如图1所示。

2.1 PXA250处理器的主要特点

(1)高性能

低功耗,高性能的32位Intel XScale处理器内核,工作频率高达400MHz;

兼容ARMv5TE架构;

采用7级超级流水线结构;

支持多媒体处理技术www.cechina.cn,采用40位累加器和16位乘法器,以增强对音频和视频的解码能力;

提供支持同步Intel StrataFlash存储器的高性能分帧和分页模式接口。

(2)低功耗

多电源管理模式;

32KB数据和32KB指令Cache;

2KB的微小数据Cache;

支持2.5V和3.3V的存储器。

(3)I/O扩展

100MHz存储器总线CONTROL ENGINEERING China版权所有,6个静态存储空间(16或32位ROM(SMROM)/Flash/SRAM),4个动态存储分区(16或32位SDRAM);

支持2个PCMCIA 或 Compact Flash槽。

(4)外围控制模块

16通道可配置DMA控制器;

LCD控制器,独有的支持对快变彩屏的DMA方式;

920kbps Bluetooth接口;

串行端口(IrDA、I2C、I2S、AC97、3个UARTs、SPI 和SSP);

USB接口;

支持MMC/SD卡。

(5)时钟控制

五种时钟源:

32.768kHz振荡器;

3.6864MHz振荡器;

可编程的内核锁相环;

95.85MHz外围固定频率锁相环;

147.46MHz固定频率锁相环。

(6)电源管理

运行模式(正常处理模式)、Turbo模式(运行于400MHZ)、空闲模式(下电)、睡眠模式(下电)。

(7)封装形式

17mm×17 mm 256脚PBGA封装。

2.2 Intel XScale内核

Intel XScale CPU内核采用带有一个增强型存储器管道的超级流水线RISC处理器架构的体系结构。这款新型高性能、低功耗的微构架兼容ARMv5TE ISA指令集(不支持浮点指令集)。这种微构架在ARM核的周围提供了指令与数据存储器管理单元,指令、数据和微小数据Cache,写缓冲、全缓冲、挂起缓冲和分支目标缓冲器,电源管理,性能监控、调试和JTAG单元以及协处理器接口,MAC协处理器和内核存储总线。

超级流水线结构是由整型管道、存储器管道和MAC管道构成。整型管道包括7级流水线结构,取指令1(分支目标缓冲器)→取指令2→译码→寄

在线会议

在线会议 论坛

论坛 专题

专题 工控直播

工控直播 新闻中心

新闻中心 子站

子站 技术

技术 社区

社区

中控时间序列大模型TPT免费有奖体验

中控时间序列大模型TPT免费有奖体验 爱德克SE2L进阶版安全激光扫描仪有奖预约演示

爱德克SE2L进阶版安全激光扫描仪有奖预约演示 剑维软件电子半导体行业白皮书有奖下载

剑维软件电子半导体行业白皮书有奖下载 魏德米勒麒麟系列产品赋能本土工业

魏德米勒麒麟系列产品赋能本土工业 Fluke 283 FC 智能万用表震撼来袭

Fluke 283 FC 智能万用表震撼来袭